Prüfstandssteuerung

mit offenem Steuerungskonzept

Für die unterschiedlichen Forschungsvorhaben ist ein eingenentwickeltes, offenes Steuerungskonzept vorhanden, das eine hohe Transparenz und beste Eingriffsmöglichkeiten bietet. Die Notwendigkeit hierfür ist in den hohe Anforderungen an die Flexibilität für Forschungsprüfstände begründet. Aus diesem Grunde handelt es sich bei der übergeordneten Prüfstandssteuerung um eine Eigenentwicklung, die entsprechend den Anforderungen der jeweiligen Forschungsvorhaben weiterentwickelt wird. Das Steuerungskonzept ist im Folgenden beschrieben. Als Beispiele dienen der Antriebsstrangprüfstand für elektrische Fahrzeugantriebe sowie der hochdynamische Verspannungsprüfstand.

Steuerungskonzept und Datenkopplung

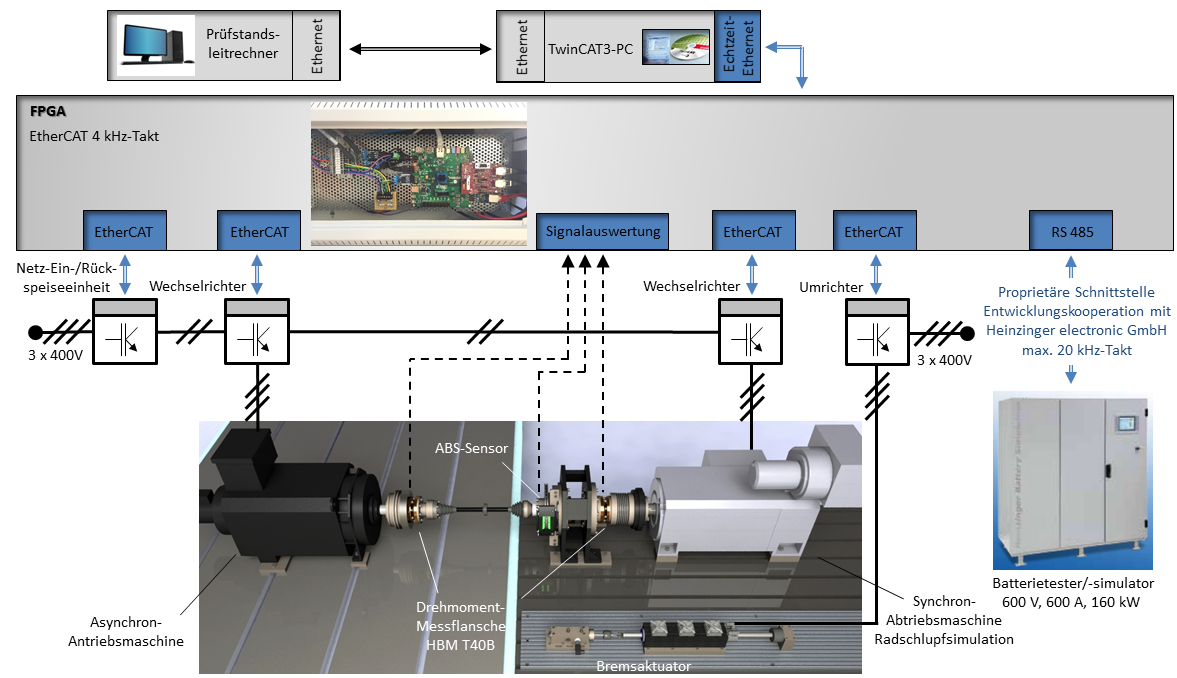

Das Steuerungskonzept basiert auf einer übergeordneten Prüfstandsteuerung, bestehend aus einem Prüfstandsleitrechner, einem Echtzeitsteuerrechner (TwinCAT3-PC) sowie einem FPGA (Field Programmable Gate Array) und den unterlagerten Wechselrichtern mitsamt der Netz-Ein-/Rückspeiseeinheit. Die Abb. 1 gibt einen Überblick über das Steuerungskonzept sowie die Datenkopplung.

Der Prüfstandsleitrechner dient zur Entwicklung von Steuerungs- und Regelungsalgorithmen sowie als Bedien- bzw. Steuerungsoberfläche.

Auf dem Echtzeitsteuerrechner läuft die Steuerungssoftware TwinCAT3 der Beckhoff Automation GmbH & Co. KG. Diese ermöglicht eine Einbindung von C/C++-, Simulink®- sowie IEC61131-Projekten. Die eigenentwickelten Steuerungs- und Regelungsalgorithmen umfassen beispielsweise die Ablaufsteuerung und Vorgabe automatisierter Prüfzyklen sowie entsprechende HiL-Modelle zur Nachbildung nicht vorhandener Prüflings-Komponenten. Überwachungen auf Grenzwerte und Übertragungsfehler mitsamt zugehörigen Fehlerreaktionen sorgen für einen sicheren Prüfstandsbetrieb. Zusätzlich sind Algorithmen zur Nachbildung von Fahrzeug- sowie Bremsfunktionen integriert (z.B. aktive Anti-Ruckel-Regelung, ABS-Regelung).

Die Programmierung erfolgt typischerweise mit Hilfe der Programmiersprache C/C++, für Tests und Rapid Prototyping werden Simulink®-Modelle eingesetzt. Ebenfalls implementiert ist zur Kommunikation mit Prüflingskomponenten eine CAN-Bus-Schnittstelle (Controller Area Network). Die Steuerungs- und Regelungsalgorithmen sind vollständig transparent und können an unterschiedliche Forschungsvorhaben angepasst werden.

Das FPGA (Field Programmable Gate Array) dient als Kommunikationsknoten und bildet einen Busmaster für die Kommunikation mit den Wechselrichtern und der Netz-Ein-/Rückspeiseeinheit. Entsprechend Abb. 1 liegt eine sternförmige Struktur vor, mit dem FPGA als Sternpunkt.

Das FPGA erzeugt einen Master-Takt (Reference Clock für die Distributed Clocks), auf den sich die Stromregeltakte der Wechselrichter aufsynchronisieren. Mit dem hochgenauen und optimierten Timing im FPGA sind Verzugszeiten bei der Datenübertragung gegenüber kommerziellen Lösungen minimiert. Die geringen und deterministischen Verzugszeiten erlauben eine hohe Regelgüte und Regeldynamik. So erfolgt beispielsweise die zeitsynchrone Abtastung der Rotordrehwinkel aller Prüfstandsmaschinen, was die Ermittlung und Regelung von Differenzverdrehwinkeln ermöglicht.

Die Taskzeit der Datenübertragung beträgt 250 µs. Entsprechend werden alle 250 µs die aktuellen Istwerte an die übergeordnete Prüfstandsteuerung gemeldet und neue Sollwerte übergeben. Die übergeordnete Prüfstandsteuerung erhält im Wesentlichen die Drehzahl- bzw. Drehwinkelsignale der einzelnen Prüfstandsmaschinen sowie die gemessenen Drehmomente bzw. weitere Sensorsignale und berechnet daraus die Sollwerte (z.B. Luftspaltdrehmomente der Elektromaschinen). Diese werden von den feldorientierten Stromregelungen der Wechselrichter in Form der drehmomentbildenden Stromkomponenten eingestellt. Die Wechselrichter arbeiten mit einer Pulsfrequenz von 8 kHz.

Eine schnelle Datenkopplung zum Batterietester/-simulator (ERS 600-600/160/M der Heinzinger electronic GmbH) erlaubt die Berechnung von komplexen Batteriemodellen in der übergeordneten Prüfstandssteuerung. Damit lässt sich die Hochvolt-Batterie eines Fahrzeuges realitätsgetreu nachbilden.

Das FPGA bietet die Möglichkeit, unterschiedliche Sensoren über eigenentwickelte Signalauswertungen anzukoppeln. Aktuell werden zwei Drehmoment-Messflansche (T40B der HBM Hottinger Baldwin Messtechnik GmbH) und ein in den mechanischen Prüfstandsaufbau integrierter fahrzeugspezifischer ABS-Raddrehzahlsensor (Robert Bosch GmbH) ausgewertet. Bei Bedarf sind zusätzliche Datenkanäle implementierbar. Die Erfassung sämtlicher Signale erfolgt zeitsynchron zum Master-Takt des FPGA‘s.

Zudem lässt sich ein Buskoppler der Firma Beckhoff Automation GmbH & Co. KG anbinden, es ist ein großes Portfolio an zusätzlichen Busklemmen verfügbar (verschiedene Bussysteme, AD- und DA-Wandler, IEPE-Interface für Beschleunigungssensoren, …). Diese werden der Prüfaufgabe entsprechend ausgewählt.

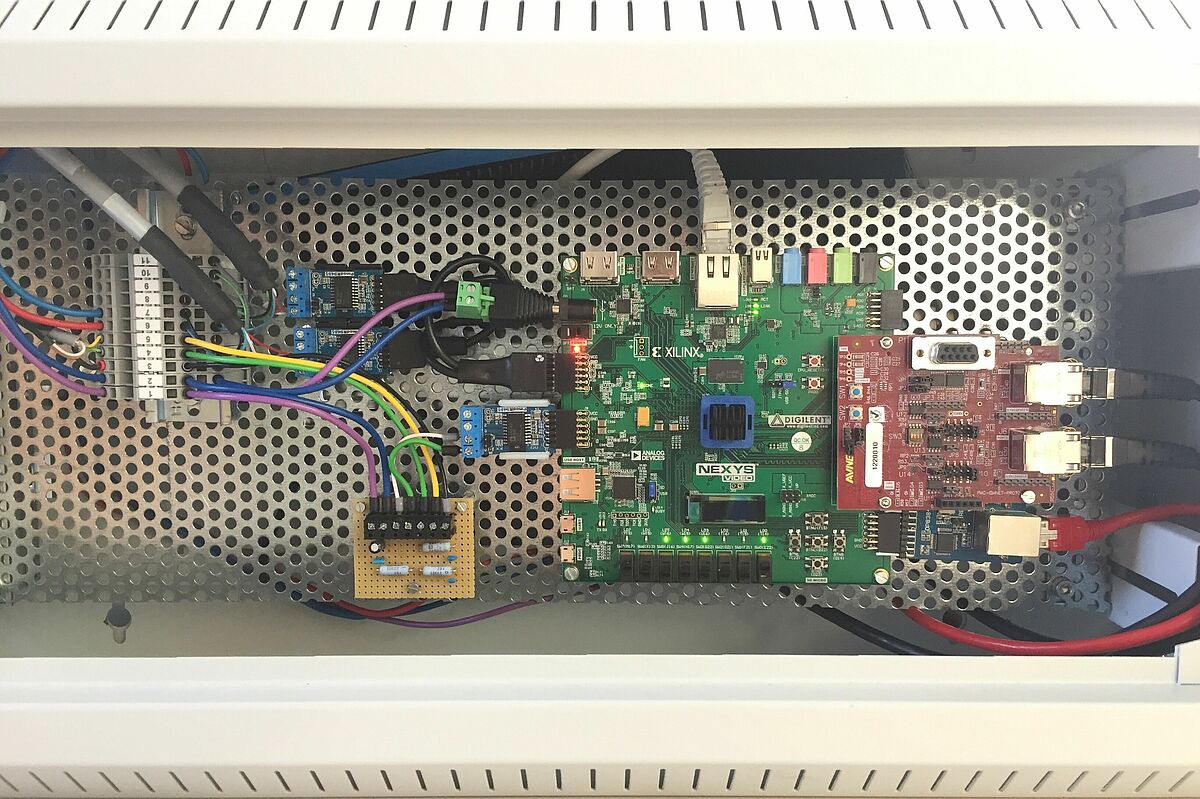

Die Programmierung des FPGA's erfolgt mit Hilfe der Hardwarebeschreibungssprache VHDL. In Abb. 2 ist die aktuelle Ausbaustufe des FPGA's dargestellt.

Steuerungsoberfläche (MMI)

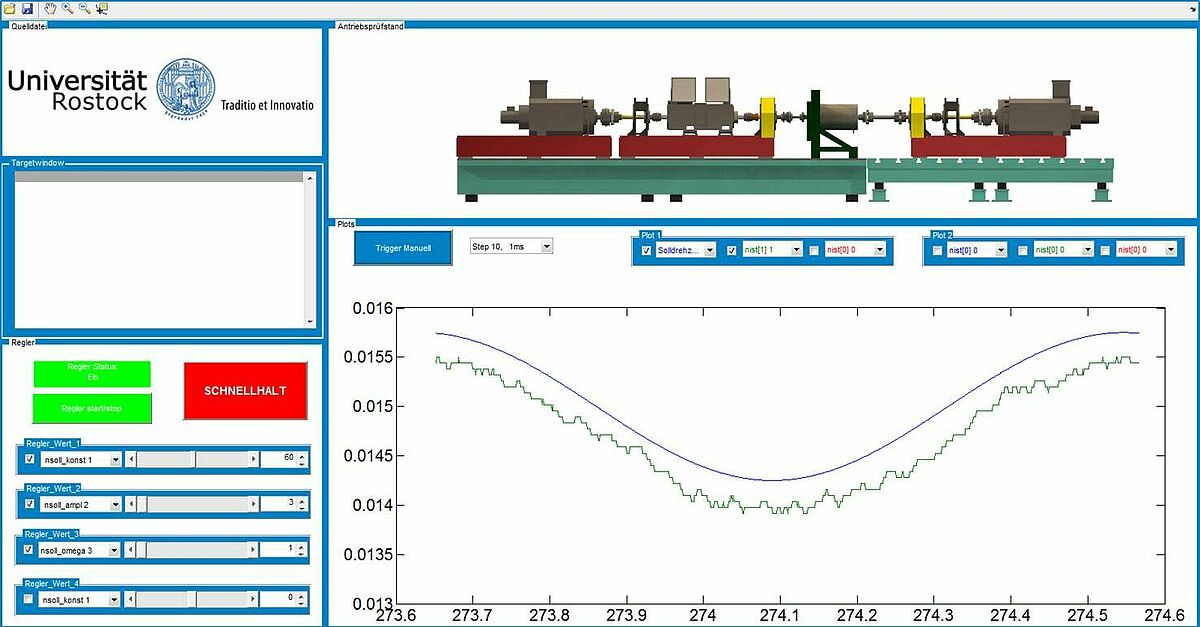

Die Steuerungsoberfläche ist unter MATLAB® erstellt und wird im Prüfstandsleitrechner abgearbeitet. Die MATLAB®-Umgebung ermöglicht eine vielfältige Weiterverarbeitung der vom Echtzeitsteuerrechner gelesenen Messdaten. Auch ein Download von Reglerparametern im Rahmen eines Regelungsentwurfs ist möglich. Daneben lassen sich automatisierte Prüfzyklen vorgeben. Die Abb. 3 zeigt beispielhaft eine einfache Version der Steuerungsoberfläche, die für Rasseluntersuchungen an Pkw-Getrieben eingesetzt wird.